- 您现在的位置:买卖IC网 > Sheet目录369 > W949D2CBJX5E (Winbond Electronics)IC LPDDR SDRAM 512MBIT 90VFBGA

�� �

�

�

�W949D6CB� /� W949D2CB�

�512Mb� Mobile� LPDDR�

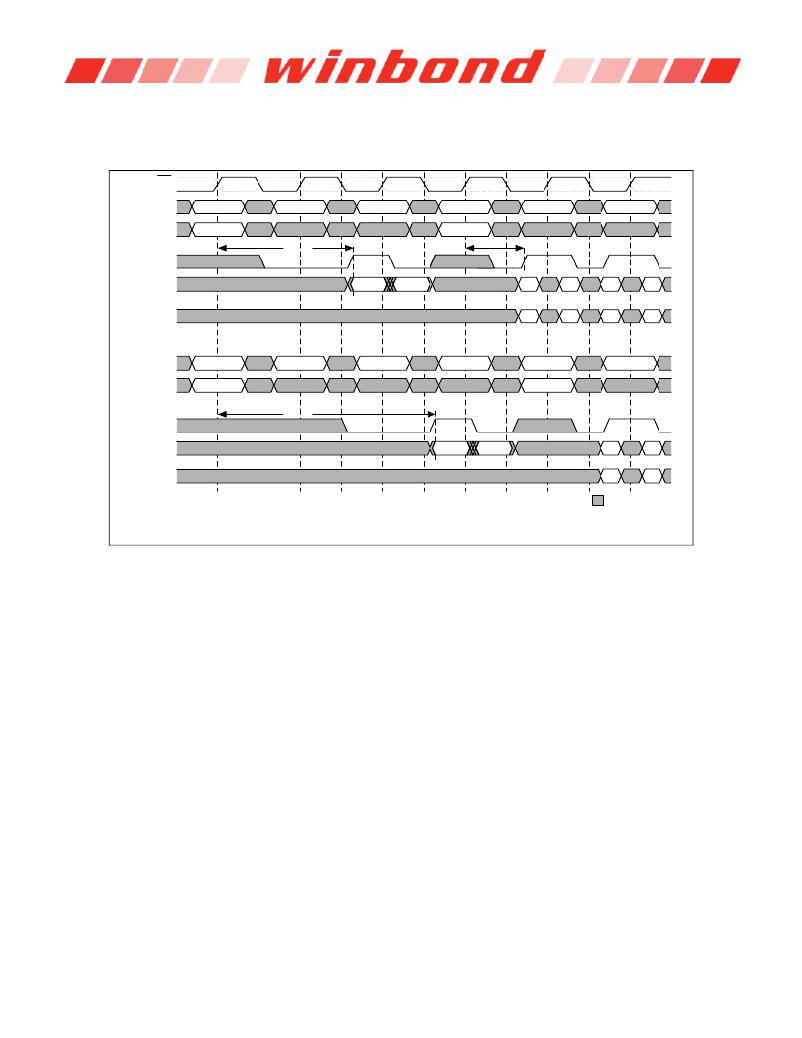

�7.5.9� Read� to� Write�

�Data� from� READ� burst� must� be� completed� or� truncated� before� a� subsequent� WRITE� command� can� be� issued.� If�

�truncation� is� necessary,� the� BURST� TERMINATE� command� must� be� used,� as� shown� in� following� figure� for� the� case�

�of� nominal� tDQSS�

�CK�

�CK�

�Command�

�READ�

�BST�

�NOP�

�WRITE�

�NOP�

�NOP�

�Address�

�BA,Col� n�

�CL=2�

�BA,Col� b�

�t� DQSS�

�DQS�

�DQ�

�DM�

�DO� n�

�Command�

�READ�

�BST�

�NOP�

�NOP�

�WRITE�

�NOP�

�Address�

�BA,Col� n�

�BA,Col� b�

�CL=3�

�DQS�

�DQ�

�DM�

�1)� DO� n� =� Data� Out� from� column� n;� DI� b=� Data� In� to� column� b�

�DO� n�

�=� Don't� Care�

�2)� Burst� length� =� 4,� 8� or� 16� in� the� cases� shown;� If� the� burst� length� is� 2,� the� BST� command� can� be� omitted�

�3)� Shown� with� nominal� tAC,� tDQSCK� and� tDQSQ�

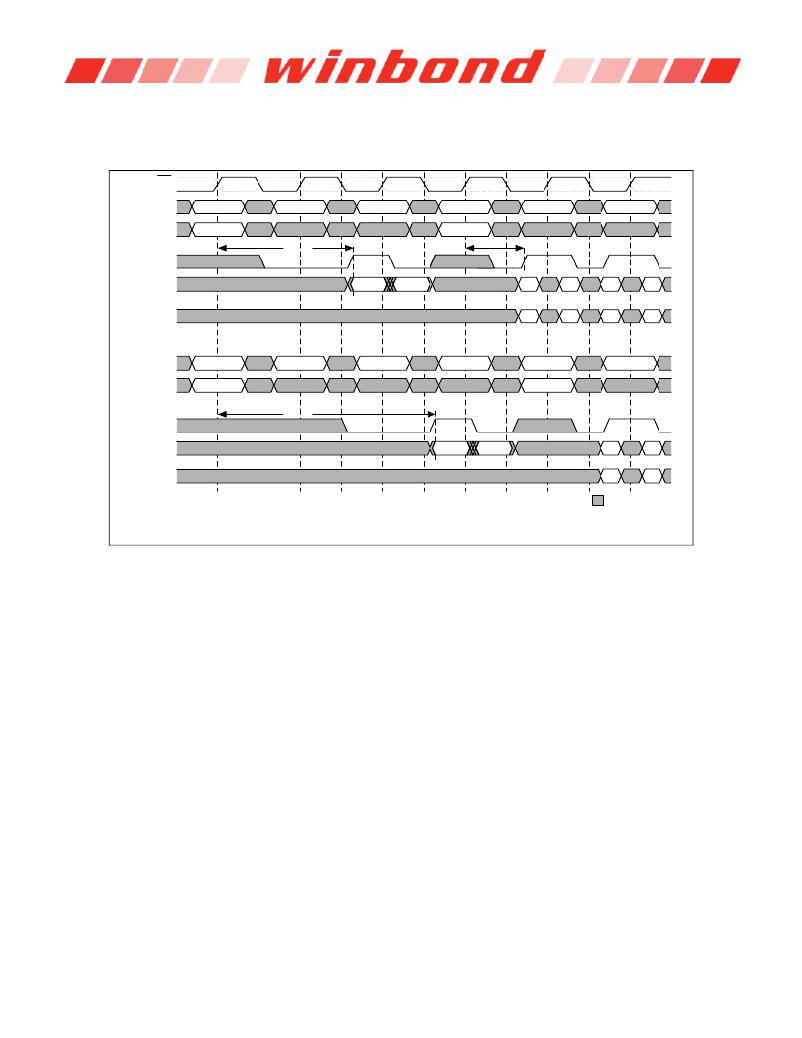

�7.5.10� Read� to� Pre-charge�

�A� Read� burst� may� be� followed� by� or� truncated� with� a� PRECHARGE� command� to� the� same� bank� (provided� Auto� Pre-�

�charge� was� not� activated).� The� PRECHARGE� command� should� be� issued� X� cycles� after� the� READ� command,�

�where� X� equal� the� number� of� desired� data-out� element� pairs.� This� is� shown� in� following� figure.� Following� the�

�PRECHARGE� command,� a� subsequent� command� to� the� same� bank� cannot� be� issued� until� t� RP� is� met.� Note� that� part�

�of� the� row� pre-charge� time� is� hidden� during� the� access� of� the� last� data-out� elements.�

�In� the� case� of� a� Read� being� executed� to� completion,� a� PRECHARGE� command� issued� at� the� optimum� time� (as�

�described� above)� provides� the� same� operation� that� would� result� from� Read� burst� with� Auto� Pre-charge� enabled.� The�

�disadvantage� of� the� PRECHARGE� command� is� that� it� requires� that� the� command� and� address� buses� be� available� at�

�the� appropriate� time� to� issue� the� command.� The� advantage� of� the� PRECHARGE� command� is� that� it� can� be� used� to�

�truncate� bursts.�

�Publication� Release� Date:� Sep,� 21,� 2011�

�-� 32� -�

�Revision� A01-007�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W971GG6JB25I

IC DDR2 SDRAM 1GBIT 84WBGA

W971GG8JB-25

IC DDR2 SDRAM 1GBIT 60WBGA

W9725G6IB-25

IC DDR2-800 SDRAM 256MB 84-WBGA

W9725G6JB25I

IC DDR2 SDRAM 256MBIT 84WBGA

W9725G6KB-25I

IC DDR2 SDRAM 256MBIT 84WBGA

W972GG6JB-3I

IC DDR2 SDRAM 2GBITS 84WBGA

W9751G6IB-25

IC DDR2-800 SDRAM 512MB 84-WBGA

W9751G6KB-25

IC DDR2 SDRAM 512MBIT 84WBGA

相关代理商/技术参数

W949D2CBJX5ETR

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 200MHZ

W949D2CBJX5I

制造商:Winbond Electronics Corp 功能描述:DRAM Chip Mobile LPDDR SDRAM 512M-Bit 16Mx32 1.8V 90-Pin VFBGA

W949D2CBJX5I TR

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 200MHZ, INDUST

W949D2CBJX6E

制造商:Winbond Electronics Corp 功能描述:DRAM Chip Mobile LPDDR SDRAM 512M-Bit 16Mx32 1.8V 90-Pin VFBGA

W949D2CBJX6ETR

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 166MHZ, 65NM

W949D2CBJX6G

制造商:WINBOND 制造商全称:Winbond 功能描述:512Mb Mobile LPDDR

W949D2KBJX5E

制造商:Winbond Electronics Corp 功能描述:512M MDDR, X32, 200MHZ 制造商:Winbond Electronics Corp 功能描述:IC MEMORY

W949D2KBJX5I

制造商:Winbond Electronics Corp 功能描述:IC MEMORY